실리콘 반도체칩 대체하는 초소형 반도체칩 기술 등 응용가능...ACS Nano 게재

UNIST·美미네소타주립대, 원자층증착법...10 나노미터 이하 채널

국제 공동 연구진이 고가의 빔 공정이 필요없는 초미세 패턴 제조 기술을 개발했다.

작은 반도체칩 안에 들어있는 수십억 개의 미세소자는 여러 층의 재료 속에 그려진 패턴 형태로 이러한 패턴 제조를 위해서는 빔으로 모양을 그리는 공정이 필요하다. 이러한 기술들은 적용의 어려움과 운용 비용이 고가인 단점이 존재해왔다.

울산과학기술원(UNIST)은 물리학과 남궁선 교수와가 미국 미네소타주립대 연구진과 함께 물질을 여러 번 얇게 입히는 공정만으로 반도체 패턴 제조가 가능한 기술을 개발했다고 24일 밝혔다.

해당 연구는 나노 재료 분야 학술지 에이씨에스 나노(ACS Nano)에 논문명 'Ultraflat Sub-10 Nanometer Gap Electrodes for Two-Dimensional Optoelectronic Devices'로 2월 24일자 온라인으로 공개될 예정이다.

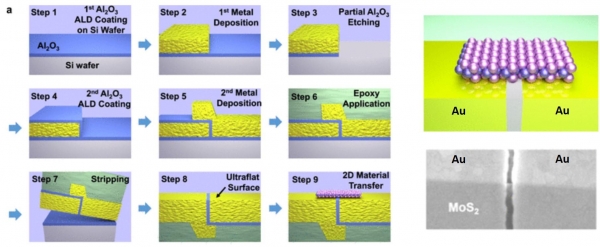

연구진들은 원자층증착법을 이용해 박막의 두께를 원자층 단위로 조절하고 실리콘 웨이퍼 크기의 넓은 면적에서 반도체 채널 길이를 정밀하게 조절할 수 있게 했다.

원자층증착법(Atomic Layer Deposition)은 박막 성장 기술의 하나로 두 개 이상의 기체 상태의 전구체 사이의 화학적 반응을 통해 넓은 영역에 균일하게 원자층 박막을 한 층식 증착시키는 기술이다.

10nm(나노미터) 이하 채널을 갖는 초미세 반도체 전극과 2차원 반도체 소자를 제작해 금속-절연체-금속 순서로 기판 위에 증착하고 갭 패턴을 만들었는데 이를 기판에서 뜯어내 뒤집으면 절연층 두께만큼 전극 간의 거리가 분리된 전극 패턴이 완성된다고 연구진을 설명했다.

전극표면은 기판에서 바로 분리됐기 때문에 표면이 매끈하다는 장점이 있기 때문에 전극 위에 2차원 반도체 물질인 이황화몰리브덴, 흑린 등을 쌓아 소자(트랜지스터)를 만들기에 적합하다고 한다.

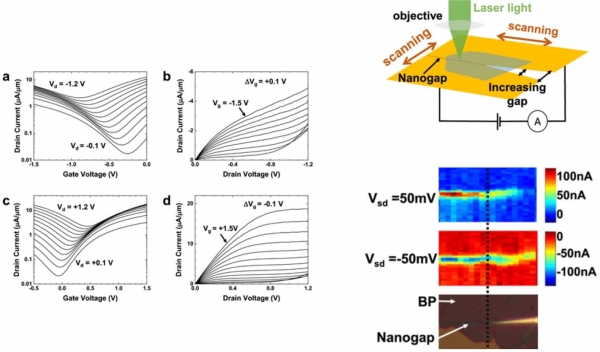

연구팀은 초고속 광통신 등에 필수적이며 빛을 전류 형태로 검출하는 소자인 트랜지스터 기반 광 검출기로도 응용해 초미세 트랜지스터 전극 사이의 강한 전기장이 빛에 의해 생성된 전하 입자들을 효과적으로 분리하고 검출 성능을 향상시켰다.

남궁선 교수는 "반도체 구조 소형화와 초소형 광통신 모듈, 광학반도체칩 개발에 도움이 될 수 있을 것"이라고 밝혔다.

포인트경제 김수철 기자